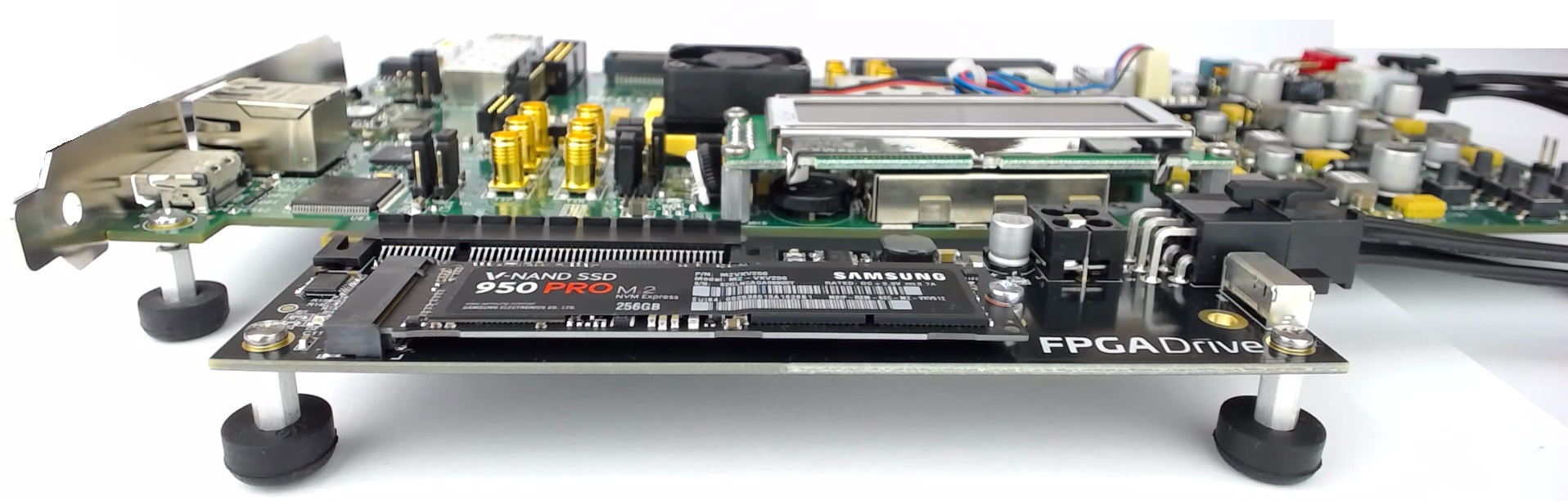

Bring-up of the first FPGA Drive with the Kintex-7 KC705 Evaluation board went nice and smoothly today. In the photo below you’ll see the KC705 and FPGA Drive adapter which is loaded with a Samsung V-NAND 950 Pro. The solid-state drive is an M.2 form factor, NVM Express, 4-lane PCI Express drive with 256GB of storage.

A little intro to NVM Express. NVM Express or NVMe is an interfacing specification for accessing SSDs over a PCI Express bus. By connecting the SSD over PCIe, it has a direct connection to the CPU which results in lower latency when compared to SATA drives, as well as increased throughput and potential for scaling (just add more lanes). PCIe SSDs can use the older AHCI interfacing standard, but due to the way that standard was designed, it can’t fully exploit the potential of modern SSDs. The NVMe specification was designed from the ground up to solve this problem.

A bit of info on the board. The FPGA Drive adapter is a 6-layer PCB. Although I’m bringing it up on the KC705 board, it has been designed for compatibility with all the Xilinx Series-7 eval boards that have PCIe edge-connectors. Although I’m using the Samsung V-NAND 950 Pro, it has been designed to carry most standard M-key M.2 devices. It contains a switching power supply which converts the incoming 12V supply to a 3.3V supply to power the SSD. It has a clock generator which supplies a 100MHz clock to both the FPGA and the SSD. The board has some logic to generate the PCIe reset signal for both FPGA and SSD.

FMC version coming soon. This version of the FPGA Drive connects to the PCIe edge connector, for applications where the FMC connectors are being used for other things - imagine being able to record gigabytes of samples from an ADC module, or Ethernet packets from the Ethernet FMC. I’ll soon present the HPC FMC version of this product, for applications where either there is no PCIe edge connector or where that connector is being used - as would be the case for an FPGA board that is plugged into a server.

Power cable. Power to the KC705 and the FPGA Drive is supplied by the same 12V adapter that comes with the KC705 (and other Xilinx eval boards for that matter). The single output connector of the adapter is converted to two parallel outputs by the black adapter cable shown below (to be supplied with the FPGA Drive).

Testing the board. After verifying the 3.3V switching power supply and current draw of the adapter board without SSD, I checked them again with the SSD and then again when connected to the KC705 - all clear. Then I tested the system with a bitstream in the Kintex-7 FPGA. The design running on the Kintex-7 contains an AXI Memory Mapped to PCI Express Bridge IP configured as a Root Port or root complex. To test the design, I ran a stand-alone application on the MicroBlaze which configures and tests the PCIe Bridge IP, then enumerates all PCIe devices found. The example application can be found in the Xilinx SDK folder here: C:\Xilinx\SDK\2015.4\data\embeddedsw\XilinxProcessorIPLib\drivers\axipcie_v3_0\examples\xaxipcie_rc_enumerate_example.c Below is a screen shot of the output of the test application. As you can see, the FPGA achieved PCIe “link up” and the application successfully enumerated the SSD end-point. In the next few days I’ll release the sources and write a tutorial showing how to build this design in Vivado and test it on the KC705.

My next task is to get the SSD functioning under a Linux operating system with the in-box NVMe driver. Unfortunately, PetaLinux 2015.4 doesn’t seem to have the NVMe driver built-in, so I’m going to have to build the kernel myself from the Xilinx sources. Update 2016-04-07: Fortunately I was wrong about that - more news to come shortly.

If you want more info about FPGA Drive, just get in touch.