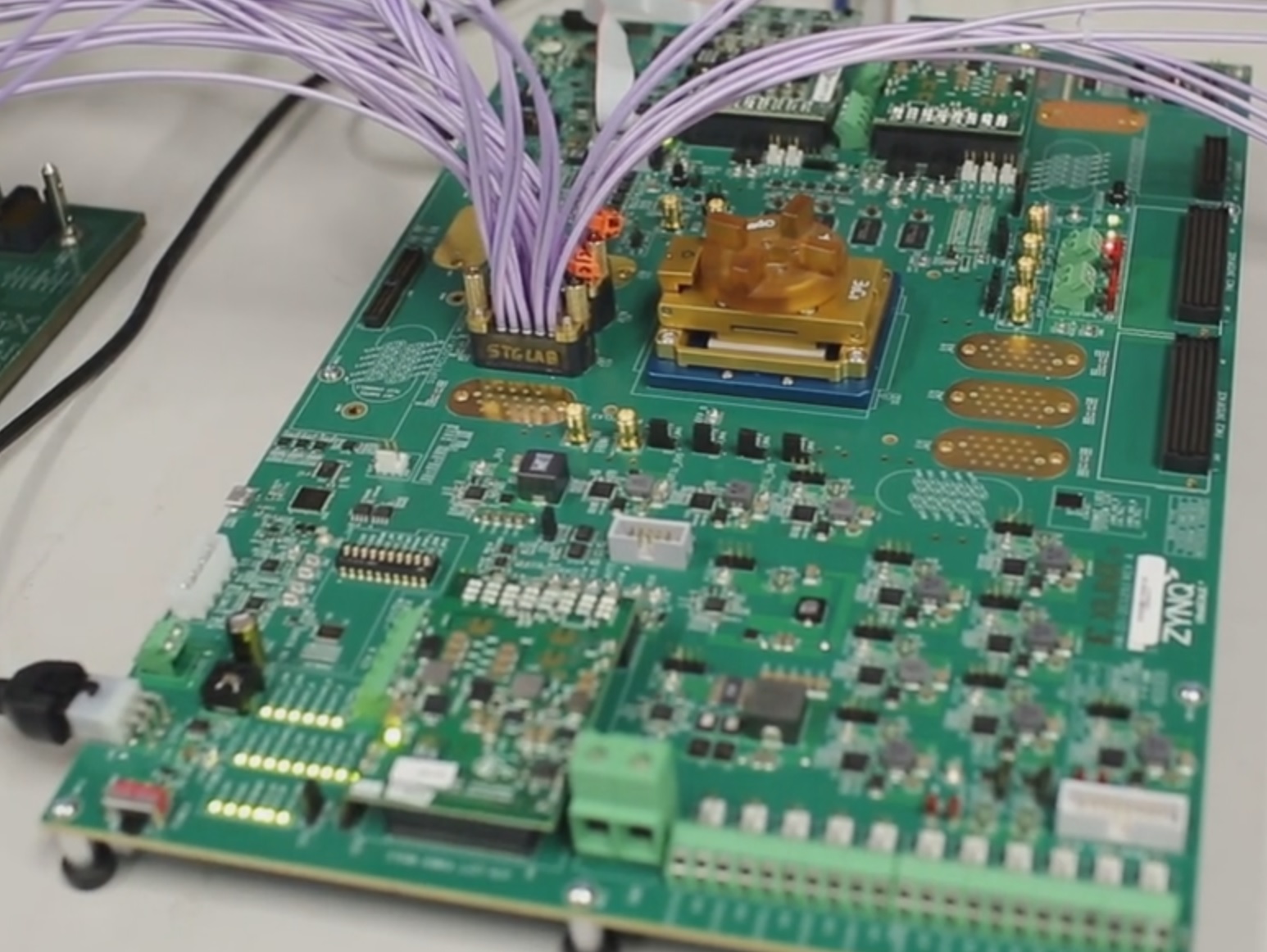

Avnet Silica was at Embedded World 2018 in Nuremburg, Germany last February demonstrating some cool industrial networking solutions such as TSN and FOSS GNU/Linux security concepts on Opsero’s Robust Ethernet FMC and the Zynq UltraScale+. Get a glimpse of the hardware at 0:54. If you saw the demo in person, I’d love to know what you thought of it.

Breakout the Zynq Ultrascale+ GEMs with Ethernet FMC

Did you know that the Zynq Ultrascale+ has 4 built-in Gigabit Ethernet MACs (GEMs)? That makes it awesome for Ethernet applications which is why I’ve just developed and shared an example design for the Zynq Ultrascale+ ZCU102 Evaluation board, armed with an Ethernet FMC to break-out those handy GEMs. The ZCU102 board has two FMC connectors, both high-pin-count (HPC), so I’ve created one basic design with two sets of constraints to choose from, depending on which FMC connector you want to use.

[Read More]

Multi-port Ethernet in PetaLinux

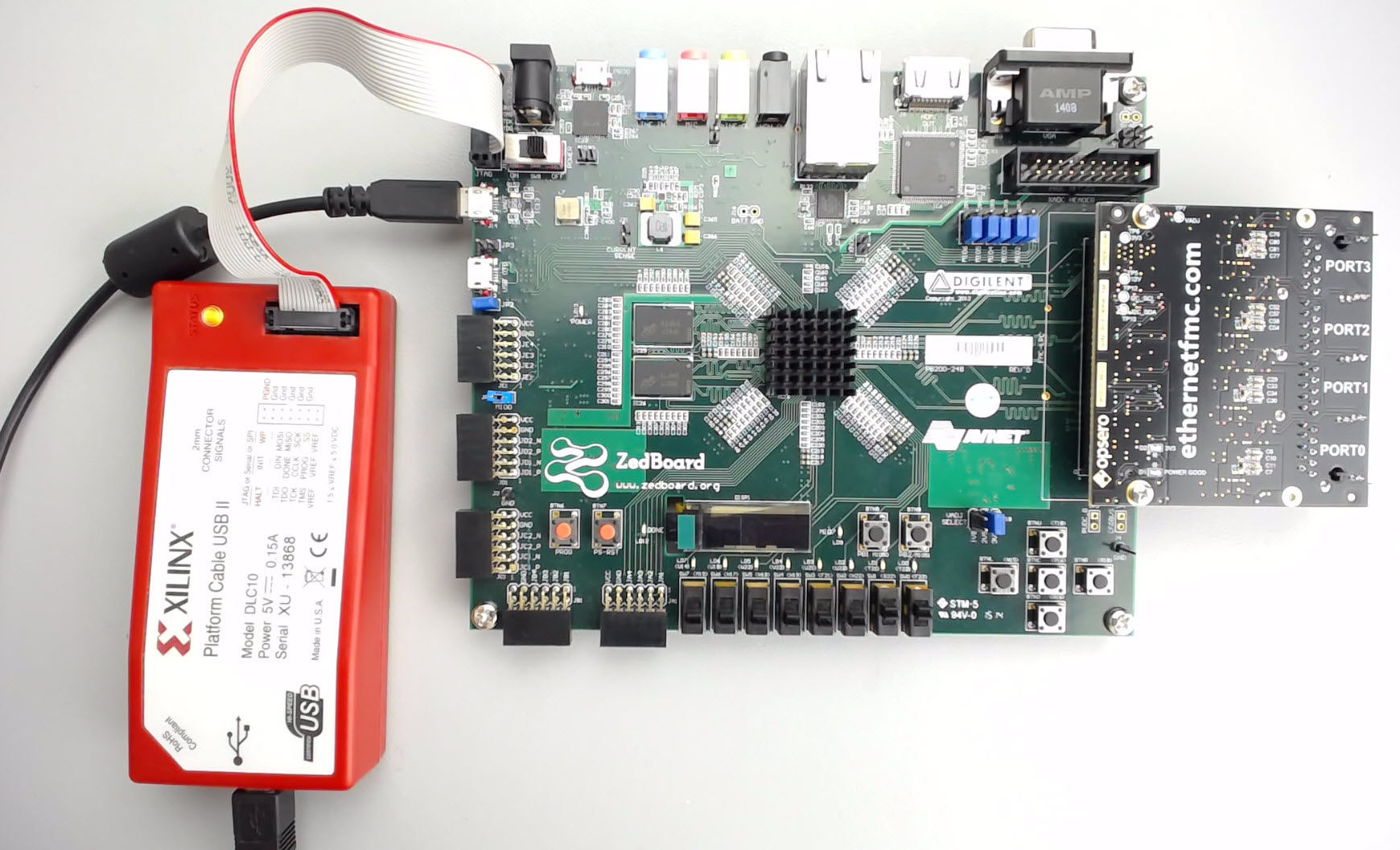

Many FPGA-based embedded designs require connections to multiple Ethernet devices such as IP cameras, and control of those devices under an operating system, typically Linux. The development of such applications can be accelerated through the use of development boards such as the ZedBoard and the Ethernet FMC. In this tutorial, we will build a custom version of PetaLinux for the ZedBoard and bring up 4 extra Ethernet ports, made available by the Ethernet FMC.

[Read More]

Running a lwIP Echo Server on a Multi-port Ethernet design

Tutorial Overview This tutorial is the follow-up to Using AXI Ethernet Subsystem and GMII-to-RGMII in a Multi-port Ethernet design. In this part of the tutorial we will generate the bitstream, export the hardware description to the SDK and then test the echo server application on our hardware. The echo server application runs on lwIP (light-weight IP), the open source TCP/IP stack for embedded systems. Our hardware platform is the Avnet ZedBoard combined with the Ethernet FMC.

[Read More]

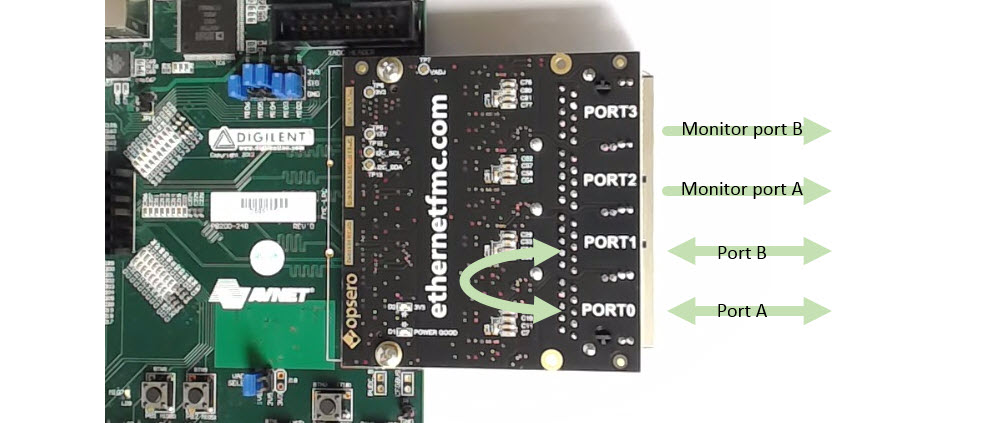

FPGA Network tap: Designing the Ethernet pass-through

When designing a network tap on an FPGA, the logical place to start is the pass-through between two Ethernet ports. In this article, I’ll discuss a convenient way to connect two Ethernet ports at the PHY-MAC interface, which will form the basis of a network tap. The pass-through will be designed in Vivado for the ZedBoard combined with an Ethernet FMC. In future articles, I’ll discuss other aspects of an FPGA network tap design, including monitor ports, packet filtering, and opportunities for hardware acceleration in the FPGA.

[Read More]

Using AXI Ethernet Subsystem and GMII-to-RGMII in a Multi-port Ethernet design

Tutorial Overview In this two-part tutorial, we’re going to create a multi-port Ethernet design in Vivado 2015.4 using both the GMII-to-RGMII and AXI Ethernet Subsystem IP cores. We’ll then test the design on hardware by running an echo server on lwIP. Our target hardware will be the ZedBoard armed with an Ethernet FMC, which adds 4 additional Gigabit Ethernet ports to our platform. Ports 0 to 2 of the Ethernet FMC will connect to separate AXI Ethernet Subsystem IPs which will be configured in DMA mode.

[Read More]

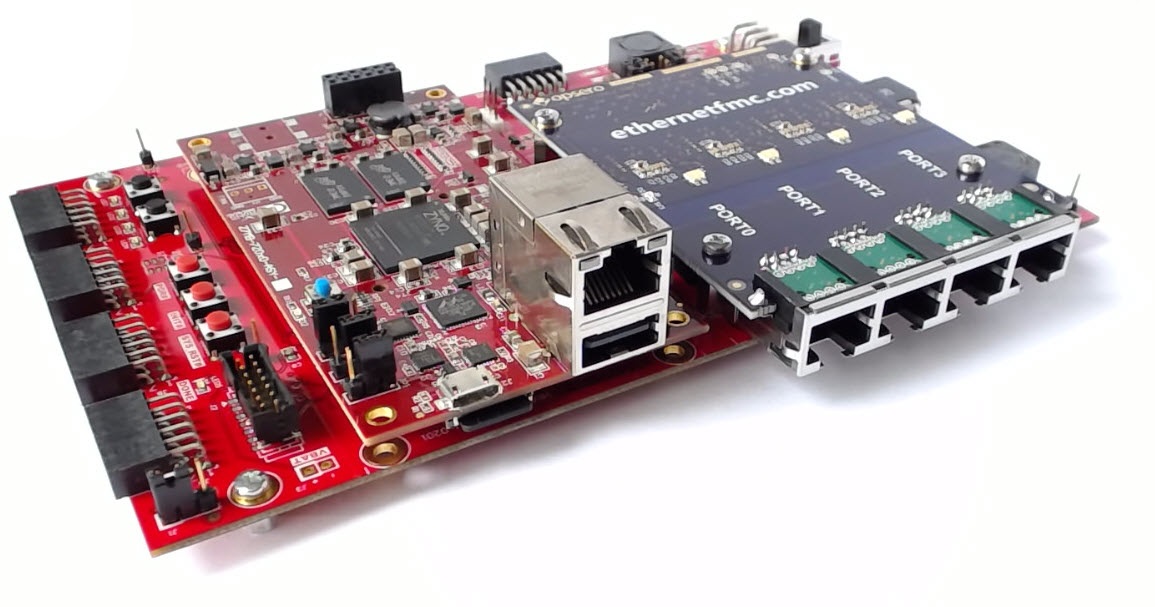

Ethernet gets robust

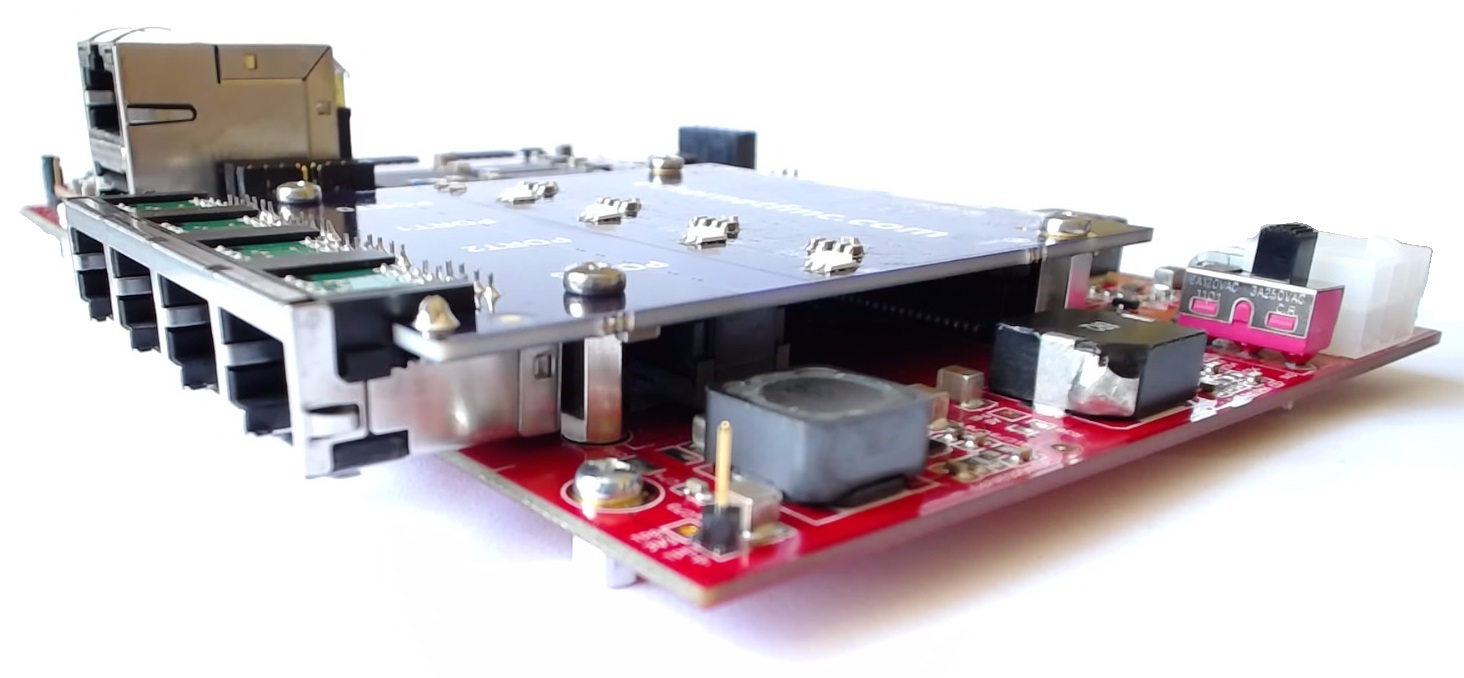

Announcing that the Robust Ethernet FMC is now in stock and available for purchase. Checkout the flashy new images of the first units, ravaging Ethernet packets in this tough new form factor.

Back in black

Here’s a look at a batch of Ethernet FMCs fresh off the production line.

Sneak look at the new Robust Ethernet FMC

Here are the first images of my new product: the Robust Ethernet FMC.

This new variation of the Ethernet FMC contains all the features of the standard version but has been designed to fit the 10mm height profile of the Vita 57.1 standard. The Robust Ethernet FMC is perfect for the more rugged gigabit Ethernet applications, and here’s why:

4 x 10mm stand-offs positioned to fit the mounting holes of the Vita 57.

[Read More]

Ethernet FMC performance benchmarks released

One question I get a lot about the Ethernet FMC is: What is the maximum throughput? It’s a good question, so I created an example design to help me get the answer. The maximum throughput test design, that you can download on Github, uses four hardware packet generators (coded in VHDL) to feed the Ethernet MACs with back-to-back packets. These packets then get sent out of the Ethernet ports and get looped back into another Ethernet port through a CAT-5 cable.

[Read More]