Many FPGA-based embedded designs require connections to multiple Ethernet devices such as IP cameras, and control of those devices under an operating system, typically Linux. The development of such applications can be accelerated through the use of development boards such as the ZedBoard and the Ethernet FMC. In this tutorial, we will build a custom version of PetaLinux for the ZedBoard and bring up 4 extra Ethernet ports, made available by the Ethernet FMC. The Vivado hardware design used in this tutorial will be very similar to the one we created in a previous tutorial titled: Using AXI Ethernet Subsystem and GMII-to-RGMII in a Multi-port Ethernet design. You don’t need to have followed that tutorial to do this one, as the Vivado project can be built from the sources on Github.

[Read More]Useful Links

- ZedBoard Product Page

- ZedBoard Board Definition Files are built into Vivado

Device

Zynq™-7000 SoC XC7Z020-CLG484-1

VADJ

The VADJ voltage is determined by jumper header J18 and can be manually set to 1.8V, 2.5V or 3.3V.

Configuration

Boot mode is determined by jumper headers labelled MIO2-MIO6.

| Boot mode | MIO6 | MIO5 | MIO4 | MIO3 | MIO2 |

|---|---|---|---|---|---|

| JTAG (cascaded) | X | 0 | 0 | 0 | 0 |

| JTAG (independent) | X | 0 | 0 | 0 | 1 |

| Quad-SPI | X | 1 | 0 | 0 | X |

| SD Card | X | 1 | 1 | 0 | X |

Notes:

- 0 = install jumper between middle pin and GND

- 1 = install jumper between middle pin and 3V3

- X = don’t care

- MIO6 determines PLL used (0) or bypassed (1)

Running a lwIP Echo Server on a Multi-port Ethernet design

Tutorial Overview

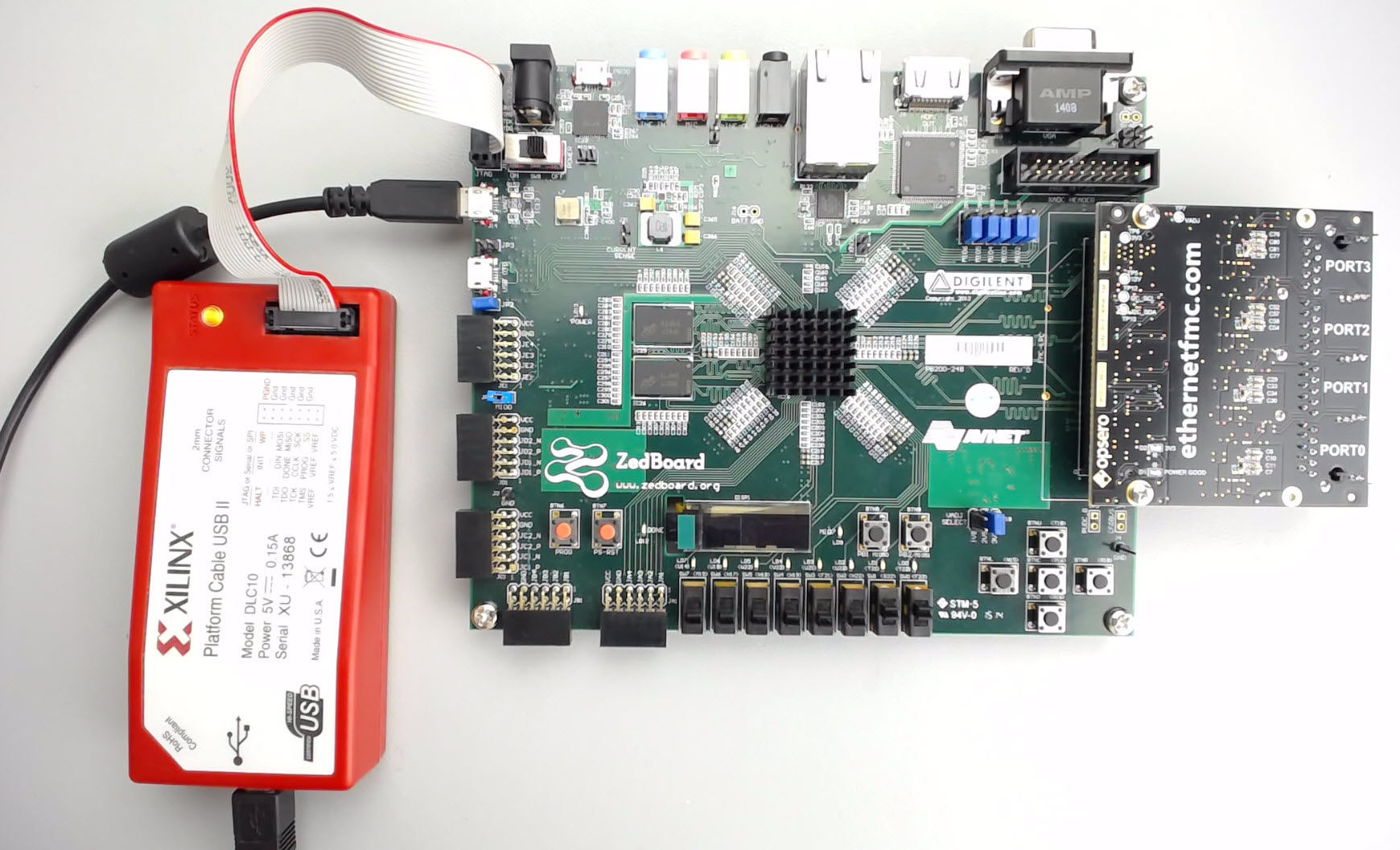

This tutorial is the follow-up to Using AXI Ethernet Subsystem and GMII-to-RGMII in a Multi-port Ethernet design. In this part of the tutorial we will generate the bitstream, export the hardware description to the SDK and then test the echo server application on our hardware. The echo server application runs on lwIP (light-weight IP), the open source TCP/IP stack for embedded systems. Our hardware platform is the Avnet ZedBoard combined with the Ethernet FMC.

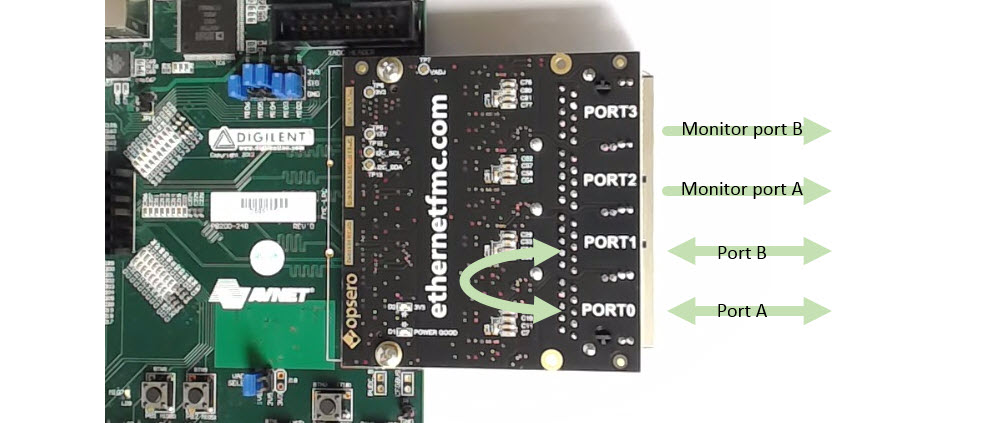

[Read More]FPGA Network tap: Designing the Ethernet pass-through

When designing a network tap on an FPGA, the logical place to start is the pass-through between two Ethernet ports. In this article, I’ll discuss a convenient way to connect two Ethernet ports at the PHY-MAC interface, which will form the basis of a network tap. The pass-through will be designed in Vivado for the ZedBoard combined with an Ethernet FMC. In future articles, I’ll discuss other aspects of an FPGA network tap design, including monitor ports, packet filtering, and opportunities for hardware acceleration in the FPGA.

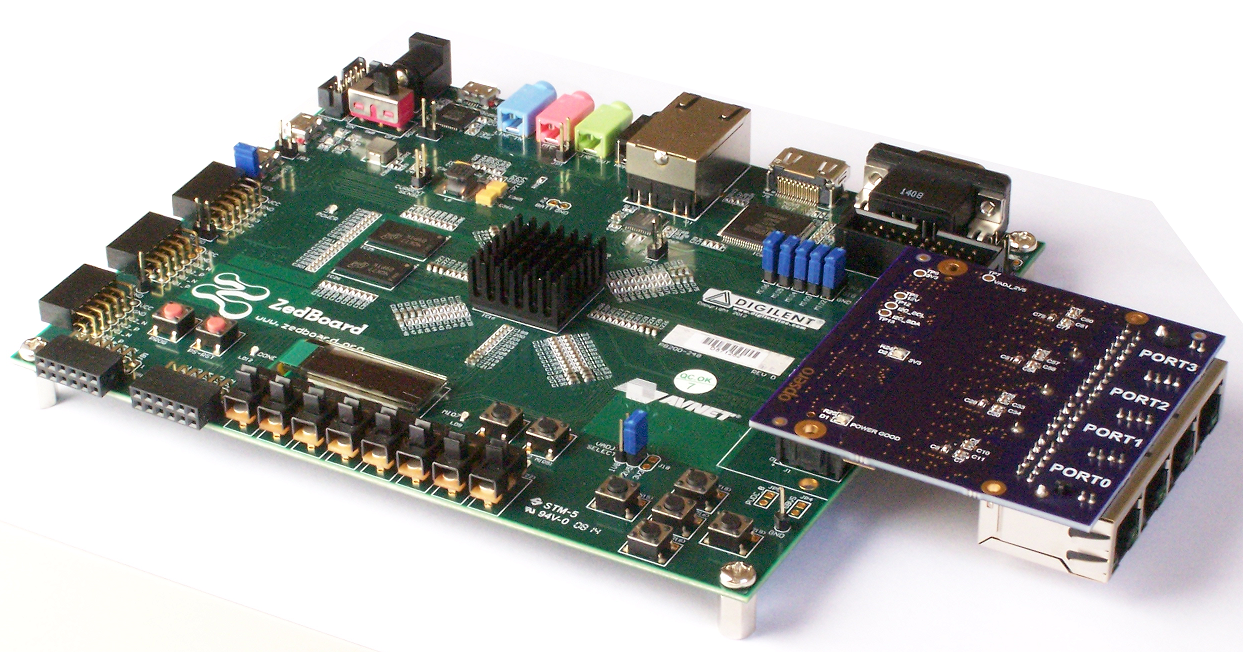

[Read More]Introducing the Quad Gigabit Ethernet FMC

Here’s the next product in Opsero’s growing lineup of FPGA I/O cards: the Quad Gigabit Ethernet FMC. This low-pin-count FMC is loaded with four Marvell Gigabit Ethernet PHYs and enables FPGA networking applications on the ZedBoard and other LPC carriers. A demo design for the ZedBoard is available on Github at the link below and further demos will become available in the next few weeks:

https://github.com/fpgadeveloper/zedboard-qgige

Look out for more details including the technical specs, schematics and more on the soon to be launched product page. (Update 2014-11-06: the product page is now open)

[Read More]A first look at a first product

After years designing products for other companies, I’ve finally designed something for my own company.

If you have a ZedBoard and you want to experiment with MGTs, now you can with my two new SERDES low-pin-count FMCs. Both boards use the DS32EL0421/DS32EL0124 serializer/deserializer devices from Texas Instruments to provide two external multi-gigabit transceivers from any standard FMC carrier regardless of whether the FPGA has internal MGTs or not. The external MGTs can transmit and receive data up to 2.5Gbps with DC-balance encoding (8b/10b) or up to 3.125Gbps without DC-balance encoding.

[Read More]Comparison of Zynq boards

If you’re interested in testing out the Zynq-7000 SoC from Xilinx there are now quite a few options available, so it comes down to a question of features vs price. Below I’ve listed the most important features of the available boards side-by-side to help you make the right decision for yourself or your company. I’ll also go into what I think of each board before we look at the boards in terms of their popularity.

[Read More]