Accelerating a Python FIR filter on the PYNQ-Z1 by offloading computation to FPGA fabric

March 22, 20182 minutes

Tutorial on creating a simple custom PYNQ overlay with an HLS adder IP and testing it via Jupyter

March 15, 20182 minutes

Step-by-step tutorial for building a custom AXI-Streaming FIFO IP in Vivado and testing it with DMA

November 1, 20177 minutes

Tutorial on connecting an NVMe SSD to an FPGA and accessing it from PetaLinux using FPGA Drive.

April 15, 201614 minutes

Tutorial on creating a Zynq-based PCIe Root Complex design in Vivado to connect an NVMe SSD.

April 14, 201613 minutes

Tutorial on creating a Microblaze-based PCIe Root Complex design in Vivado to connect an NVMe SSD.

April 13, 201618 minutes

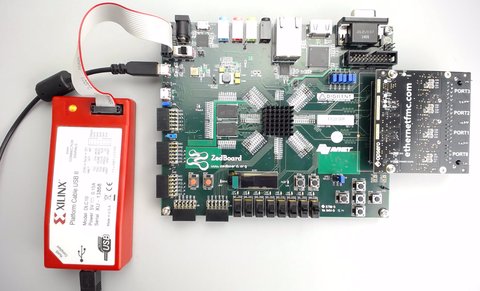

Testing a multi-port Ethernet design by running a lwIP echo server on the ZedBoard with Ethernet FMC.

January 5, 201611 minutes

Building a multi-port Gigabit Ethernet design in Vivado using AXI Ethernet and GMII-to-RGMII IP cores.

December 8, 201516 minutes

Tutorial on setting up and testing the AXI DMA engine in a Vivado design targeting the MicroZed.

August 6, 20149 minutes

Tutorial on creating a custom AXI IP block in Vivado with integrated VHDL code on the MicroZed.

August 4, 20148 minutes