Title here

Summary here

A curated list of open-source PYNQ projects, overlays, and ports to various platforms

March 29, 20182 minutes

Demonstrating FPGA-accelerated 2D filter and dilate on 720p video achieving 60fps on the PYNQ-Z1

March 28, 20181 minute

Accelerating a Python FIR filter on the PYNQ-Z1 by offloading computation to FPGA fabric

March 22, 20182 minutes

Tutorial on creating a simple custom PYNQ overlay with an HLS adder IP and testing it via Jupyter

March 15, 20182 minutes

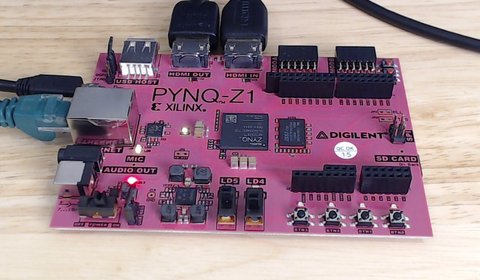

Introduction to the PYNQ-Z1 board and using Python with Jupyter to program the Zynq SoC

February 27, 20183 minutes