Building a base Vivado design for the Arty A7 board with hello world and lwIP echo server in SDK

November 8, 20173 minutes

Creating a Vivado design for the MYIR Z-turn Zynq SoM and running hello world and lwIP echo server

October 18, 20173 minutes

Updated video tutorial on using the AXI DMA IP in Vivado 2017.2 with a MicroZed Zynq design

October 11, 201716 minutes

A cheat sheet of useful Tcl commands and tricks for automating Vivado and Xilinx SDK workflows

November 1, 20165 minutes

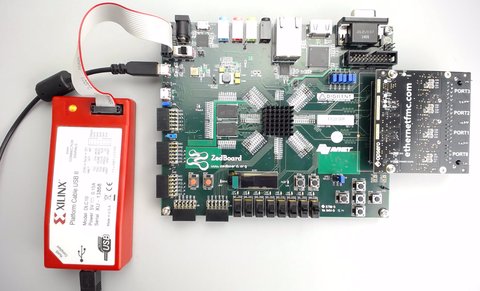

Testing a multi-port Ethernet design by running a lwIP echo server on the ZedBoard with Ethernet FMC.

January 5, 201611 minutes

Tutorial on setting up and testing the AXI DMA engine in a Vivado design targeting the MicroZed.

August 6, 20149 minutes

Tips for modifying BSP code in Xilinx SDK without losing changes during a clean rebuild

May 28, 20141 minute

Tutorial on creating a hello-world application for the Zynq ARM processor using Xilinx SDK

February 27, 20145 minutes

Tutorial on writing a Microblaze software application using Xilinx SDK 13.1

June 28, 20114 minutes