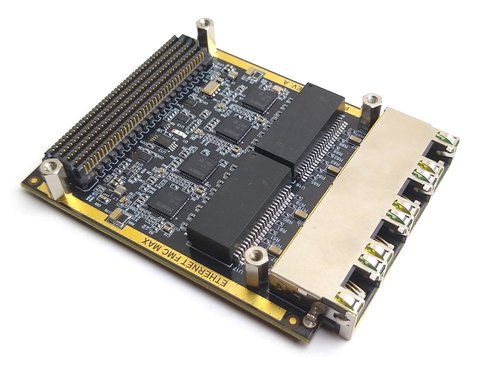

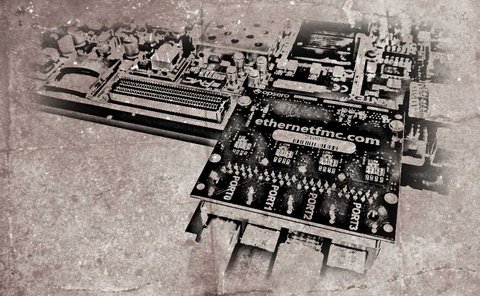

Opsero's new gigabit Ethernet FMC with SGMII

October 9, 20245 minutes

A reference design that you can build and test

October 8, 202410 minutes

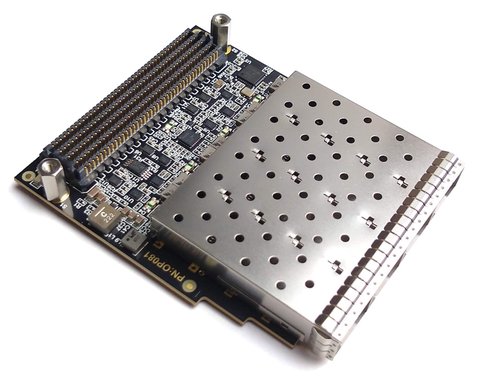

High-speed Ethernet connectivity for FPGAs

July 16, 202410 minutes

A fresh approach to getting more from FMC

April 3, 202413 minutes

State machine based Ethernet on FPGA

May 1, 20215 minutes

Modularizing the TEMAC example design

April 20, 20219 minutes

How to do it on an FPGA and why

February 16, 202113 minutes

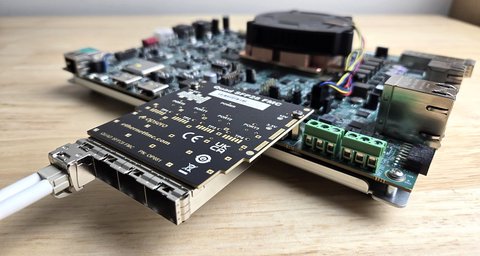

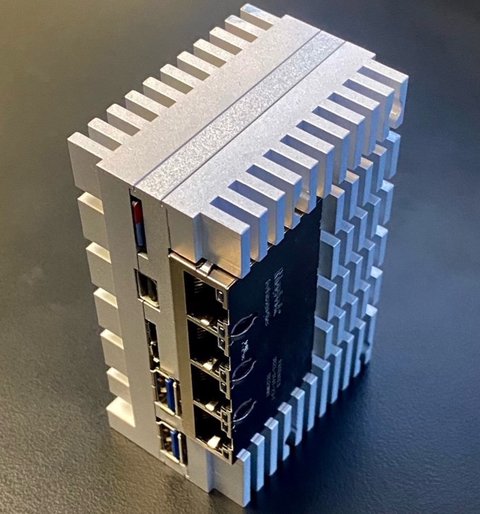

Photos of a custom passive heatsink solution for the Ultra96 and its Ethernet mezzanine

December 10, 20201 minute

Using Iperf to measure Gigabit Ethernet throughput on Ultra96 with PetaLinux, reaching 940 Mbps

July 17, 20193 minutes

Short video introduction to the 96B Quad Ethernet Mezzanine for Ultra96

June 12, 20191 minute