State machine based Ethernet on FPGA

May 1, 20215 minutes

Modularizing the TEMAC example design

April 20, 20219 minutes

How to do it on an FPGA and why

February 16, 202113 minutes

IntelliProp tests their NVMe Host Accelerator IP on FPGA Drive achieving up to 2000 MB/s read speeds

October 23, 20162 minutes

Benchmarking NVMe SSD read/write speeds on KC705 and PicoZed running PetaLinux

July 2, 20164 minutes

Tutorial on connecting an NVMe SSD to an FPGA and accessing it from PetaLinux using FPGA Drive.

April 15, 201614 minutes

Tutorial on creating a Microblaze-based PCIe Root Complex design in Vivado to connect an NVMe SSD.

April 13, 201618 minutes

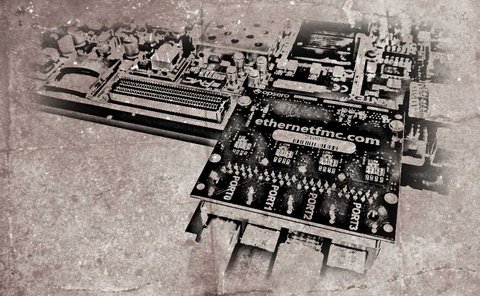

Bringing up the first FPGA Drive prototype with a Samsung NVMe SSD on the KC705 evaluation board.

March 31, 20164 minutes

Comparing Xilinx 7 Series FPGA evaluation boards for PCI Express hardware acceleration

March 12, 20142 minutes