Back in black

Posted on July 18, 2015

| Jeff Johnson

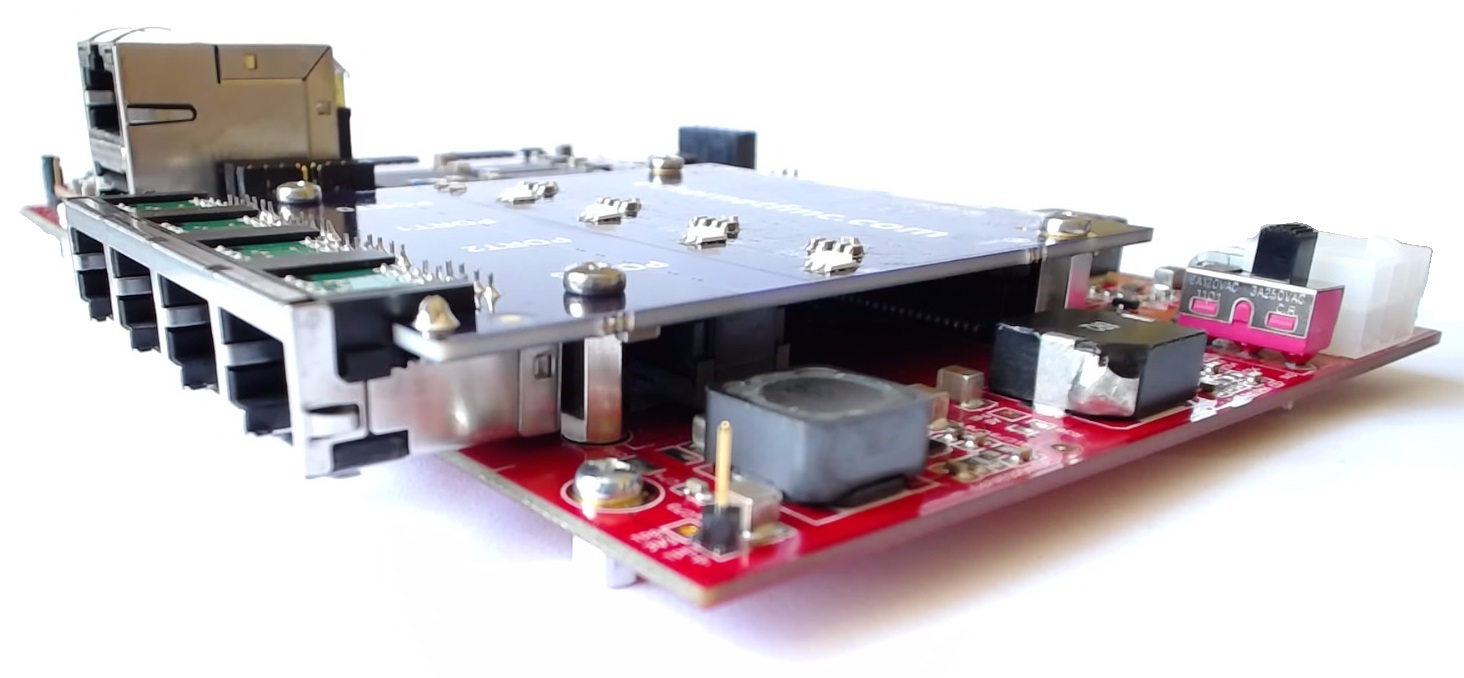

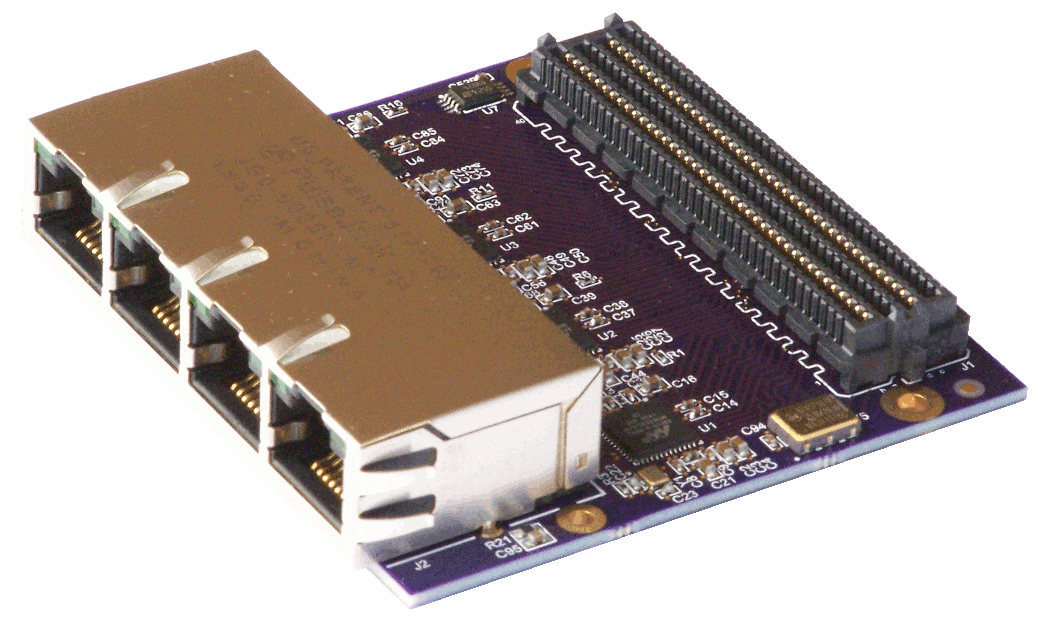

Here’s a look at a batch of Ethernet FMCs fresh off the production line.

Sneak look at the new Robust Ethernet FMC

Posted on June 10, 2015

| Jeff Johnson

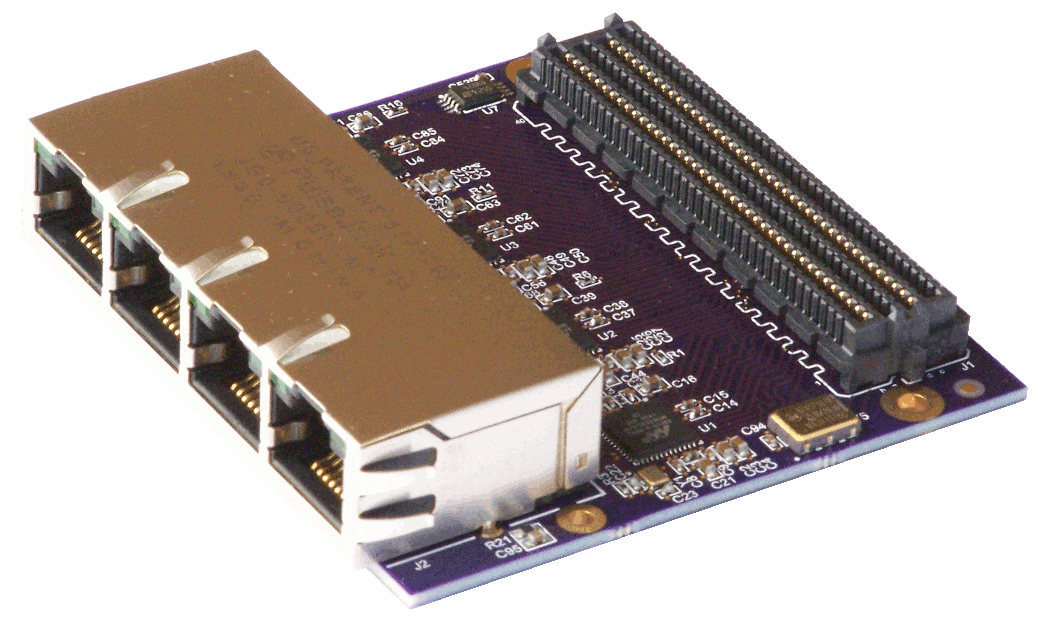

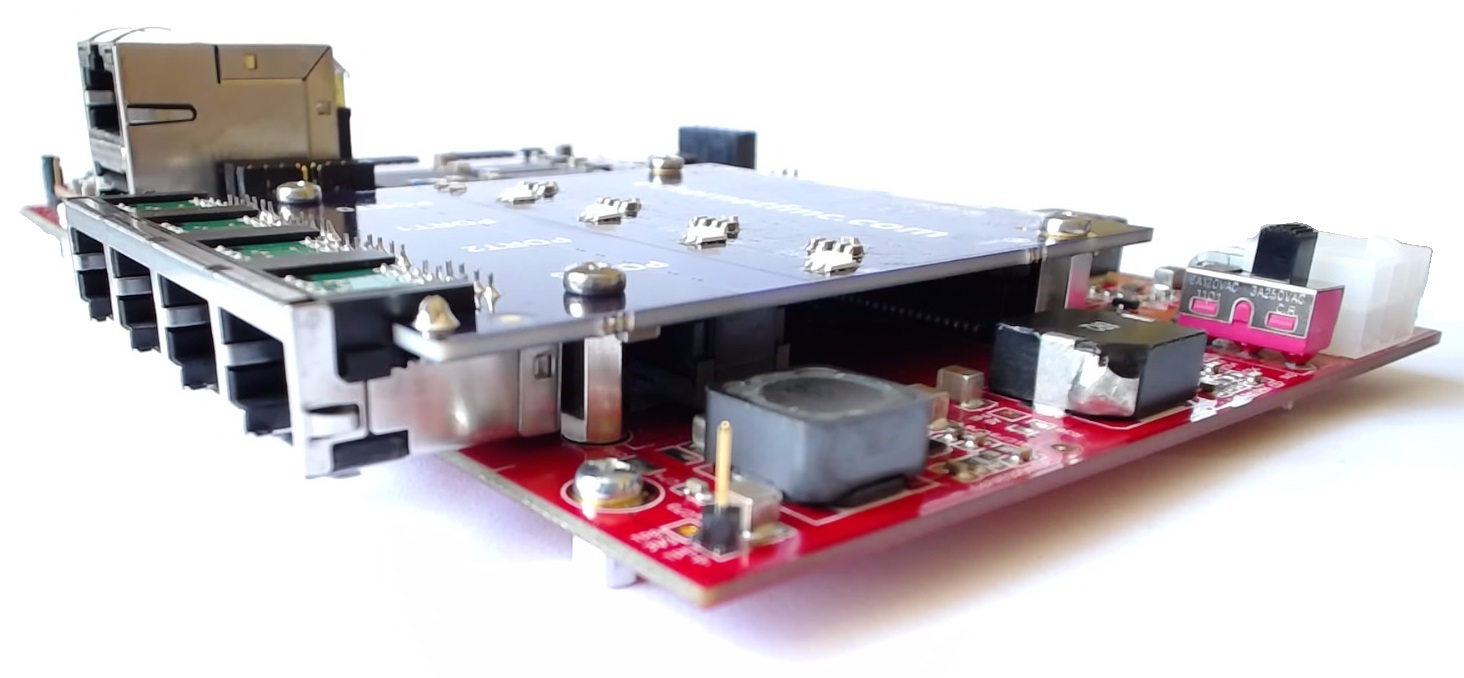

Here are the first images of my new product: the Robust Ethernet FMC.

This new variation of the Ethernet FMC contains all the features of the standard version but has been designed to fit the 10mm height profile of the Vita 57.1 standard. The Robust Ethernet FMC is perfect for the more rugged gigabit Ethernet applications, and here’s why:

4 x 10mm stand-offs positioned to fit the mounting holes of the Vita 57.

[Read More]

1.8V Version Ethernet FMC now available

Posted on April 16, 2015

| Jeff Johnson

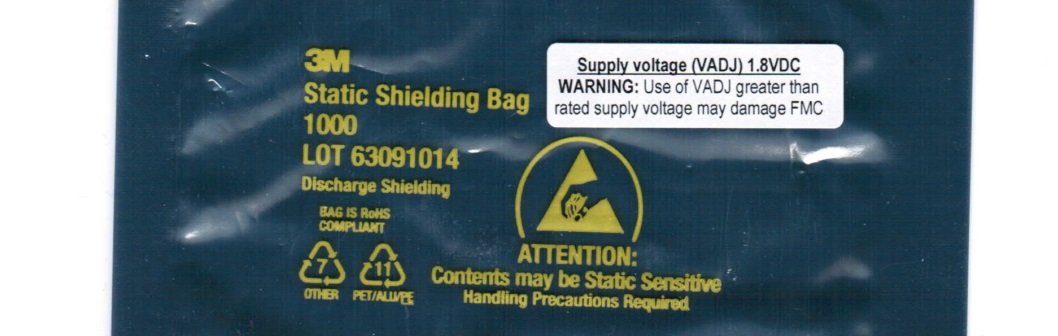

I recently received and tested the first 1.8V Ethernet FMCs and they are now available to buy on ethernetfmc.com. There are two main reasons why you’d actually want a 1.8V version: Firstly, some carriers only support VADJ of 1.8V (such as the VC707 and VC709). Secondly, some customers need to match it with another 1.8V FMC on a dual-FMC carrier.

Releasing the new version didn’t come without headaches. Most FMC carriers on the market have a 2.

[Read More]

Ethernet FMC performance benchmarks released

Posted on January 15, 2015

| Jeff Johnson

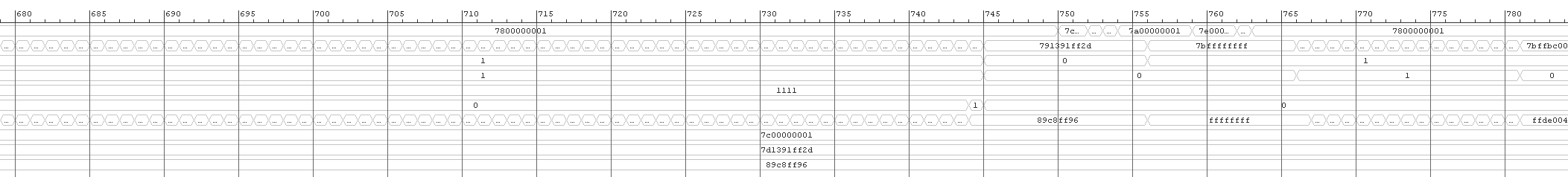

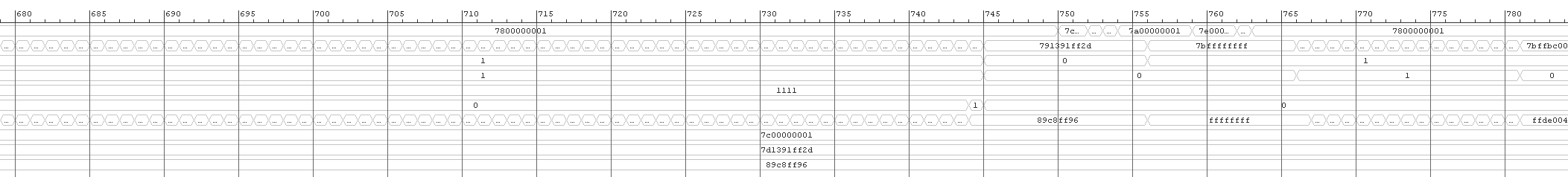

One question I get a lot about the Ethernet FMC is: What is the maximum throughput? It’s a good question, so I created an example design to help me get the answer. The maximum throughput test design, that you can download on Github, uses four hardware packet generators (coded in VHDL) to feed the Ethernet MACs with back-to-back packets. These packets then get sent out of the Ethernet ports and get looped back into another Ethernet port through a CAT-5 cable.

[Read More]

Ethernet FMC supports Xilinx Dev Boards

Posted on January 11, 2015

| Jeff Johnson

Support for the Xilinx Series-7 development boards AC701, KC705, VC707, ZC702 and ZC706 has been added to the Ethernet FMC product page. Now you can use the Ethernet FMC on any one of these boards and support up to 8 x gigabit Ethernet ports! That’s right, the KC705, VC707 and ZC702 have two FMC connectors allowing you to plug in two Ethernet FMCs, enabling 8 independent ports.

AC701 - supports 1 x Ethernet FMC (4-ports) KC705 - supports 2 x Ethernet FMCs (8-ports) VC707 - supports 2 x Ethernet FMCs (8-ports) VC709 - supports 1 x Ethernet FMC (4-ports) ZC702 - supports 2 x Ethernet FMCs, but there’s only enough FPGA resources to configure the 8 MACs with FIFOs (not DMAs).

[Read More]

Ethernet FMC first units shipped

Posted on December 17, 2014

| Jeff Johnson

Today I’m excited to announce that the first Ethernet FMCs were shipped! I would like to say thanks to all those who pre-ordered the Ethernet FMC, thanks for your patience and confidence and I hope the product enables you to develop new and exciting technologies in the networking space.

I’ve had an insanely busy last few weeks trying to organize the production of the boards, testing the boards, as well as working out the packaging, labeling and shipping materials.

[Read More]

Ethernet FMC is now available

Posted on November 3, 2014

| Jeff Johnson

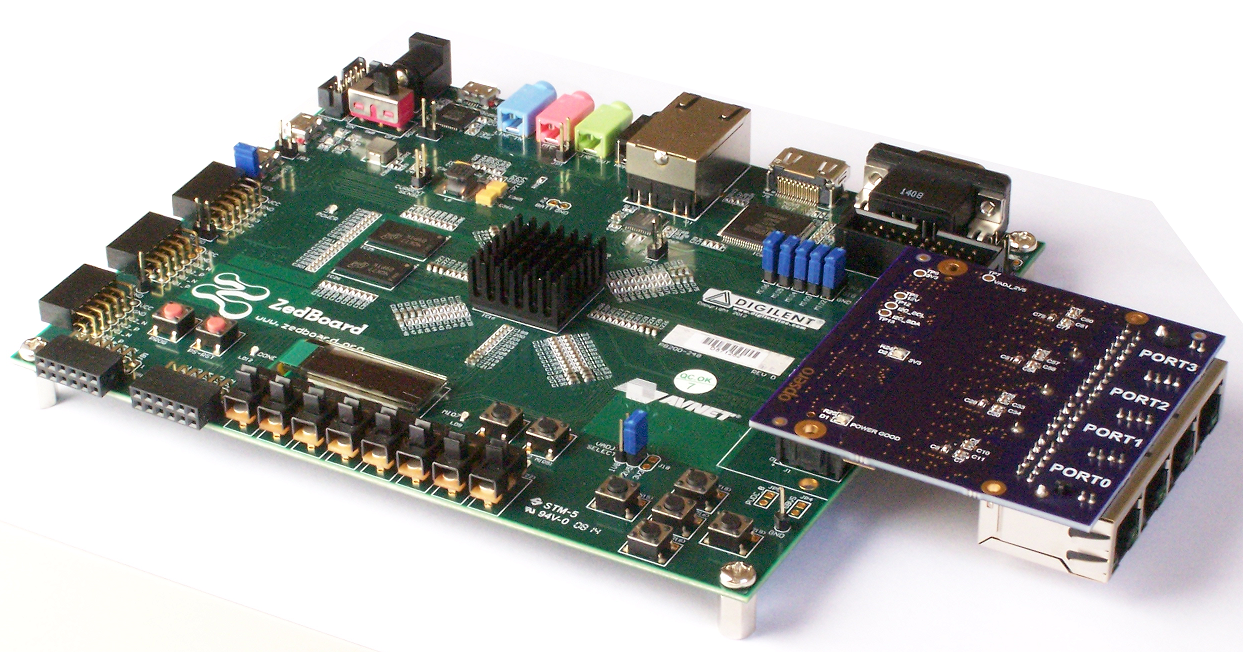

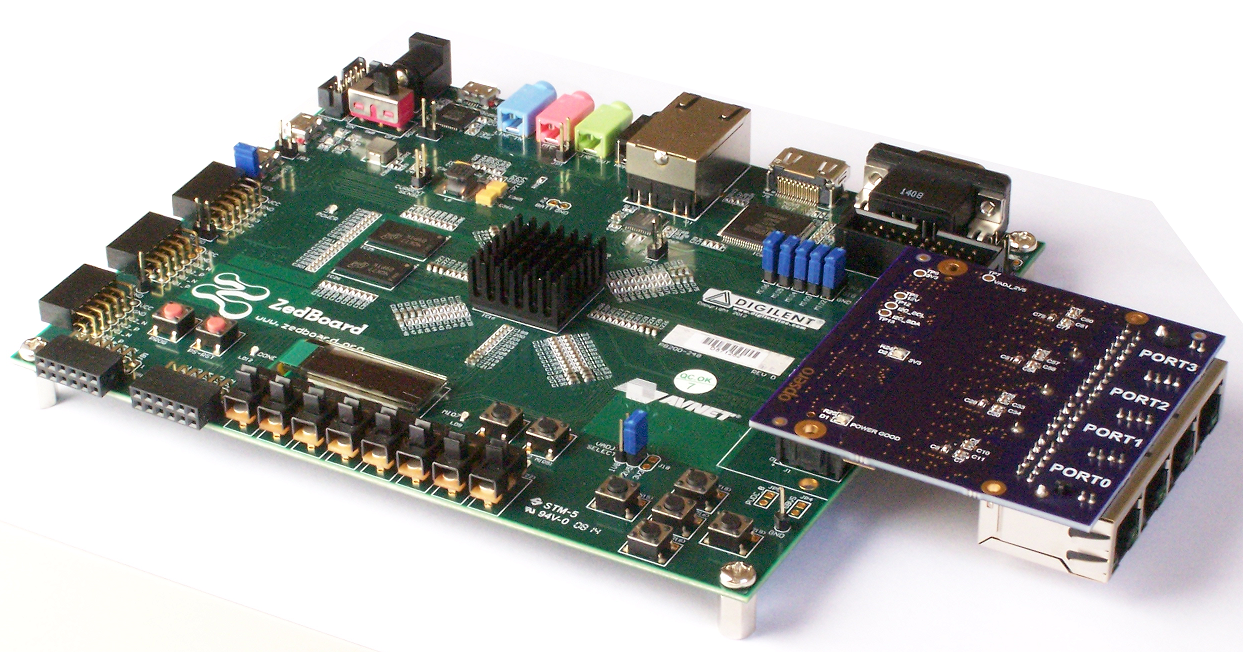

Announcing that the new Ethernet FMC, a Quad Gigabit Ethernet FPGA Mezzanine Card (FMC) is now available to buy. The board is designed for easy integration with the ZedBoard, with open-source example designs so you can start designing your product sooner. The low-pin-count FMC features 4 Marvell PHYs, a 125MHz oscillator and a quad RJ45 with integrated magnetics.

The Ethernet FMC is compliant to the Vita 57.1 FMC standard except for its height (due to the RJ45 connector) and its length.

[Read More]

Introducing the Quad Gigabit Ethernet FMC

Posted on October 13, 2014

| Jeff Johnson

Here’s the next product in Opsero’s growing lineup of FPGA I/O cards: the Quad Gigabit Ethernet FMC. This low-pin-count FMC is loaded with four Marvell Gigabit Ethernet PHYs and enables FPGA networking applications on the ZedBoard and other LPC carriers. A demo design for the ZedBoard is available on Github at the link below and further demos will become available in the next few weeks:

https://github.com/fpgadeveloper/zedboard-qgige

Look out for more details including the technical specs, schematics and more on the soon to be launched product page.

[Read More]

Comparison of Zynq boards

Posted on March 4, 2014

| Jeff Johnson

If you’re interested in testing out the Zynq-7000 SoC from Xilinx there are now quite a few options available, so it comes down to a question of features vs price. Below I’ve listed the most important features of the available boards side-by-side to help you make the right decision for yourself or your company. I’ll also go into what I think of each board before we look at the boards in terms of their popularity.

[Read More]

Aurora to Ethernet Bridge

Posted on September 24, 2009

| Jeff Johnson

Tutorial Overview

In the last tutorial we implemented the embedded Tri-mode Ethernet MAC and tested it by looping back Ethernet packets and monitoring them with Wireshark. In this tutorial, we will again implement the EMAC but this time we will link it to an Aurora core, to implement an Aurora to Ethernet Bridge. With the bridge, we can link two PCs as shown in the diagram below.

To connect the EMAC and Aurora cores we have to use two FIFOs to cross clock domains.

[Read More]