Running multi-camera YOLOv5 on Zynq UltraScale+ using a Hailo-8 AI accelerator via FPGA Drive FMC

February 15, 202419 minutes

Measuring NVMe SSD read/write speeds on the ZCU106 with FPGA Drive FMC under PetaLinux

December 2, 20196 minutes

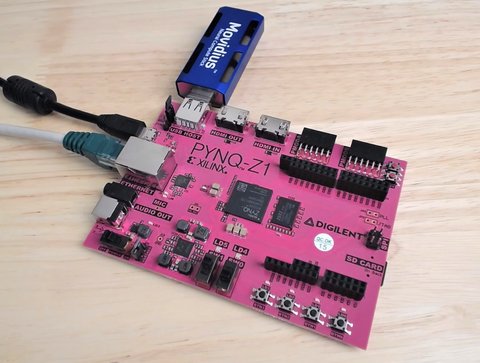

Guide to connecting and configuring the Intel Movidius NCS with the PYNQ-Z1 for AI inference

April 20, 20187 minutes

Demonstrating FPGA-accelerated 2D filter and dilate on 720p video achieving 60fps on the PYNQ-Z1

March 28, 20181 minute

Accelerating a Python FIR filter on the PYNQ-Z1 by offloading computation to FPGA fabric

March 22, 20182 minutes

Tutorial on creating a simple custom PYNQ overlay with an HLS adder IP and testing it via Jupyter

March 15, 20182 minutes

IntelliProp tests their NVMe Host Accelerator IP on FPGA Drive achieving up to 2000 MB/s read speeds

October 23, 20162 minutes

Red Hat and FPGA vendors plan to define a standard software interface for FPGA accelerator boards.

February 17, 20162 minutes

Comparing Xilinx 7 Series FPGA evaluation boards for PCI Express hardware acceleration

March 12, 20142 minutes