A tech blog on FPGA design by Jeff Johnson

A curated list of open-source PYNQ projects, overlays, and ports to various platforms

March 29, 20182 minutes

Demonstrating FPGA-accelerated 2D filter and dilate on 720p video achieving 60fps on the PYNQ-Z1

March 28, 20181 minute

Accelerating a Python FIR filter on the PYNQ-Z1 by offloading computation to FPGA fabric

March 22, 20182 minutes

Avnet Silica demos TSN and industrial networking on the Ethernet FMC at Embedded World 2018

March 17, 20181 minute

Tutorial on creating a simple custom PYNQ overlay with an HLS adder IP and testing it via Jupyter

March 15, 20182 minutes

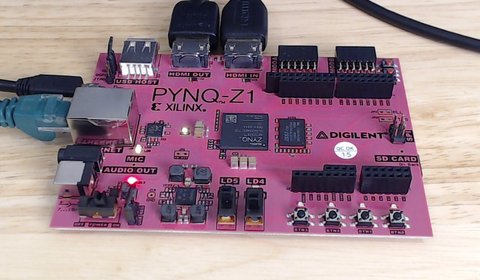

Introduction to the PYNQ-Z1 board and using Python with Jupyter to program the Zynq SoC

February 27, 20183 minutes

IntelliProp demonstrates 3200 MB/s read speeds with their NVMe IP on an Intel Arria 10 and FPGA Drive

February 26, 20181 minute

Building and booting a PetaLinux project on the Arty A7 board with network connectivity

November 15, 20175 minutes

Building a base Vivado design for the Arty A7 board with hello world and lwIP echo server in SDK

November 8, 20173 minutes

Step-by-step tutorial for building a custom AXI-Streaming FIFO IP in Vivado and testing it with DMA

November 1, 20177 minutes