A tech blog on FPGA design by Jeff Johnson

Handy quick reference cards for FPGA dev boards covering boot modes, part numbers, and settings

December 9, 20202 minutes

And onto Hugo

December 3, 20204 minutes

Step-by-step guide to building a PYNQ v2.5 SD image for the Ultra96 board

December 15, 20195 minutes

Clean install on a virtual machine

December 13, 20195 minutes

Measuring NVMe SSD read/write speeds on the ZCU106 with FPGA Drive FMC under PetaLinux

December 2, 20196 minutes

Using Iperf to measure Gigabit Ethernet throughput on Ultra96 with PetaLinux, reaching 940 Mbps

July 17, 20193 minutes

Short video introduction to the 96B Quad Ethernet Mezzanine for Ultra96

June 12, 20191 minute

Announcing a 4-port Gigabit Ethernet mezzanine card designed for the Ultra96 board

February 18, 20198 minutes

Bringing up the 3 Gigabit Ethernet ports on the MYIR MYD-Y7Z010 with Vivado and SDK

May 4, 201810 minutes

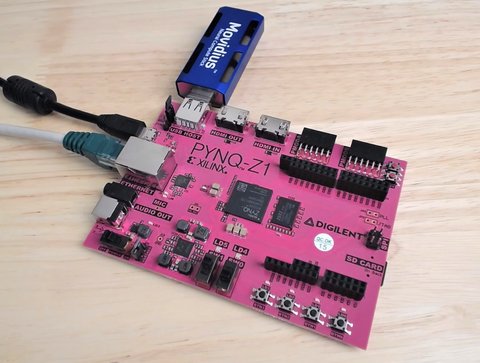

Guide to connecting and configuring the Intel Movidius NCS with the PYNQ-Z1 for AI inference

April 20, 20187 minutes