A tech blog on FPGA design by Jeff Johnson

With the objective of customizing it

May 19, 202313 minutes

Guide to downloading and running Certified Ubuntu 20.04 LTS on the ZCU106 board

May 18, 20235 minutes

On Ubuntu 20.04

May 11, 20234 minutes

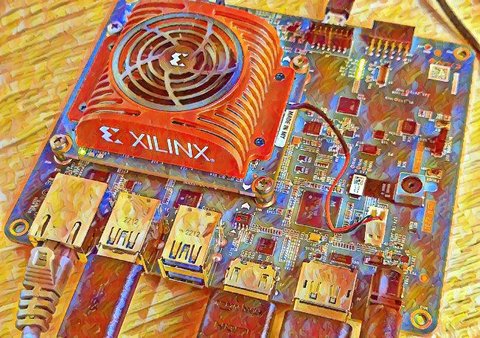

Introducing the Camera FMC product line for connecting MIPI cameras to FPGA development boards

March 1, 20235 minutes

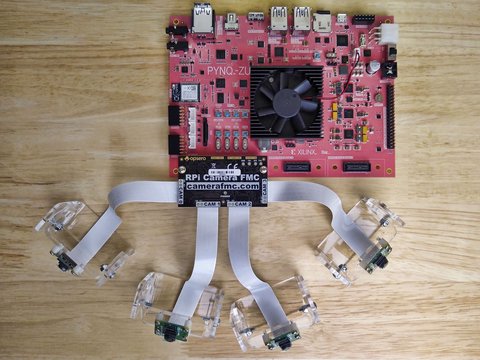

Preview of the RPi Camera FMC for connecting 4 Raspberry Pi cameras to Zynq UltraScale+ boards

February 3, 20233 minutes

Steps to update the Kria SoM boot firmware for Ubuntu 22.04 and the latest PYNQ release

November 11, 20226 minutes

Walkthrough for installing and configuring PYNQ on the Kria KV260 Vision AI Starter Kit

November 10, 20228 minutes

A categorized repository of FPGA and MPSoC development boards with specs and pricing

October 17, 20224 minutes

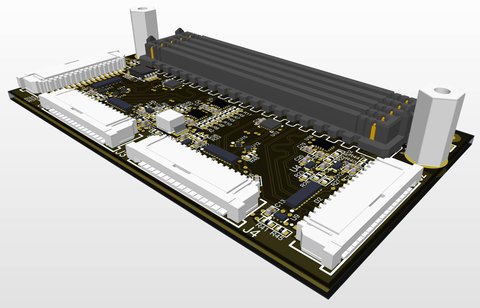

Upgrading the FPGA Drive FMC PCB design to support PCIe Gen4 with low-loss board materials

December 20, 20217 minutes

State machine based Ethernet on FPGA

May 1, 20215 minutes